# HE/UE910, UL865 Digital Voice Interface Application Note

80000NT10050A Rev. 6 - 2014-04-16

# **APPLICABILITY TABLE**

|                         | SW Versions |

|-------------------------|-------------|

| HE910 Family            |             |

| HE910 <sup>1</sup>      | 12.00.xx3   |

| HE910-GA                | 12.00.xx3   |

| HE910-EUR               | 12.00.xx3   |

| HE910-NAR               | 12.00.xx3   |

| UE/UL Family (Embedded) |             |

| UE910-EUR               | 12.00.xx4   |

| UE910-NAR               | 12.00.xx4   |

| UL865-EUR               | 12.00.xx4   |

| UL865-NAR               | 12.00.xx4   |

| UL865-N3G               | 12.00.xx4   |

**Note:** the features described in the present document are provided by the products equipped with the software versions equal or higher than the versions shown in the table. See also the Document History chapter.

$<sup>^{\</sup>rm 1}$  HE910 is the "type name" of the products marketed as HE910-G & HE910-DG

#### SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Telit assumes no liability resulting from any inaccuracies or omissions in this document, or from use of the information obtained herein. The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies or omissions. Telit reserves the right to make changes to any products described herein and reserves the right to revise this document and to make changes from time to time in content hereof with no obligation to notify any person of revisions or changes. Telit does not assume any liability arising out of the application or use of any product, software, or circuit described herein; neither does it convey license under its patent rights or the rights of others.

It is possible that this publication may contain references to, or information about Telit products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Telit intends to announce such Telit products, programming, or services in your country.

#### **Copyrights**

This instruction manual and the Telit products described in this instruction manual may be, include or describe copyrighted Telit material, such as computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and its licensors certain exclusive rights for copyrighted material, including the exclusive right to copy, reproduce in any form, distribute and make derivative works of the copyrighted material. Accordingly, any copyrighted material of Telit and its licensors contained herein or in the Telit products described in this instruction manual may not be copied, reproduced, distributed, merged or modified in any manner without the express written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a product.

#### **Computer Software Copyrights**

The Telit and 3<sup>rd</sup> Party supplied Software (SW) products described in this instruction manual may include copyrighted Telit and other 3<sup>rd</sup> Party supplied computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and other 3<sup>rd</sup> Party supplied SW certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Telit or other 3<sup>rd</sup> Party supplied SW computer programs contained in the Telit products described in this instruction manual may not be copied (reverse engineered) or reproduced in any manner without the express written permission of Telit or the 3<sup>rd</sup> Party SW supplier. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit or other 3<sup>rd</sup> Party supplied SW, except for the normal non-exclusive, royalty free license to use that arises by operation of law in the sale of a product.

#### USAGE AND DISCLOSURE RESTRICTIONS

#### **License Agreements**

The software described in this document is the property of Telit and its licensors. It is furnished by express license agreement only and may be used only in accordance with the terms of such an agreement.

#### **Copyrighted Materials**

Software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without prior written permission of Telit

#### **High Risk Materials**

Components, units, or third-party products used in the product described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life Support, or Weapons Systems (High Risk Activities"). Telit and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such High Risk Activities.

#### **Trademarks**

TELIT and the Stylized T Logo are registered in Trademark Office. All other product or service names are the property of their respective owners.

Copyright © Telit Communications S.p.A.

### **Contents**

| 1. | Intr  | oduction                       | . 7 |

|----|-------|--------------------------------|-----|

|    | 1.1.  | Scope                          | . 7 |

|    | 1.2.  | Audience                       | . 7 |

|    | 1.3.  | Contact Information, Support   | . 7 |

|    |       | Related Documents              |     |

|    | 1.5.  | Document History               |     |

|    | 1.6.  | Abbreviations and Acronyms     |     |

| 2. | DVI   | Overview                       | . 9 |

| 3. | DVI   | Bus                            | 10  |

| 4. | DVI   | AT Commands                    | 11  |

|    | 4.1.  | AT#DVI                         | 11  |

|    | 4.2.  | AT#DVIEXT                      | 12  |

| 5. | DVI   | Setting Examples               | 13  |

| ļ  | 5.1.  | Normal Mode (I <sup>2</sup> S) | 14  |

|    | 5.1.  | 1. Module is Master            | 14  |

|    | 5.1.2 | 2. Module is Slave             | 17  |

|    | 5.2.  | Burst Mode (PCM)               |     |

|    | 5.2.  |                                |     |

|    | 5.2.2 |                                |     |

| 6. | Anr   | nex                            | 25  |

|    | 6.1.  | I <sup>2</sup> S Overview      | 25  |

|    | 6.2.  | Schematic                      | 27  |

# Figures

| fig. 1: Example of Digital Voice Interface Use                                     | 9  |

|------------------------------------------------------------------------------------|----|

| fig. 2: Master and Slave Configurations                                            |    |

| fig. 3: Telit Module/Codec Connections                                             | 13 |

| fig. 4: DVI Configurations                                                         | 13 |

| fig. 5: Module is Master/Normal mode/N bits per sample/Dual Mono                   | 14 |

| fig. 6: Module is Master/Normal Mode/16 bits per sample/Dual Mono/ <edge>=0</edge> | 16 |

| fig. 7: Module is Slave/Normal Mode/24 bits per sample/Dual Mono/ <edge>=0</edge>  | 18 |

| fig. 8: Module is Master/Burst mode/N bits per Sample/Mono Mode                    | 19 |

| fig. 9: Module is Master/Burst Mode/16 bits per Sample/Mono Mode/ <edge>=1</edge>  | 21 |

| fig. 10: Module is Slave/Burst Mode/N bits per Sample/Mono Mode                    | 22 |

| fig. 11: Module is Slave/Burst Mode/16 bits per Sample/Mono Mode/ <edge>=1</edge>  | 24 |

| fig. 12: I <sup>2</sup> S bus configurations                                       |    |

| fig. 13: Schematic for Reference Design                                            | 27 |

|                                                                                    |    |

| Tables                                                                             |    |

|                                                                                    |    |

| Tab. 1: DVI Signals                                                                | 10 |

| Tab. 2: DVI Configuration via AT#DVI command                                       |    |

| Tab. 3: DVI Audio Format configuration via AT#DVIEXT command                       |    |

| Tab. 4: BitClockFrequency generated by the module in Master/Normal Mode            | 14 |

| Tab. 5: BitClockFrequency in Burst Mode                                            |    |

### 1. Introduction

The present document provides the reader with a guideline concerning the setting and use of the Digital Voice Interface developed on the Telit's modules families shown in the Applicability Table.

### 1.1. Scope

This Application Note covers the configurations of the Digital Voice Interface, e.g.: the selections of the voice sampling frequency, the bit number of the voice sample, the audio formats, etc. In addition, the document shows some configurations of a popular Audio Codec connected to the Module. These activities are accomplished via I<sup>2</sup>S and I<sup>2</sup>C buses; the hardware characteristics of the two buses are beyond the scope of the document.

### 1.2. Audience

The document is intended for those users that need to develop applications dealing with signal voice in digital format.

# 1.3. Contact Information, Support

For general contact, technical support, to report documentation errors and to order manuals, contact Telit Technical Support Center (TTSC) at:

TS-EMEA@telit.com

TS-NORTHAMERICA@telit.com

TS-LATINAMERICA@telit.com

TS-APAC@telit.com

#### Alternatively, use:

http://www.telit.com/en/products/technical-support-center/contact.php

For detailed information about where you can buy the Telit Modules or for recommendations on accessories and components visit:

#### http://www.telit.com

To register for product news and announcements or for product questions contact Telit Technical Support Center (TTSC).

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and suggestions for improvements.

Telit appreciates feedback from the users of our information.

## 1.4. Related Documents

- [1] HE910 Hardware User Guide, 1vv0300925

- [2] MAX9867 Ultra-Low Power Stereo Audio Codec, MAXIM

- [3] HE910/UE910/UL865 AT Commands Reference Guide, 80378ST10091A

- [4] UE910 Hardware User Guide, 1vv0301012

- [5] UL865 Hardware User Guide, 1vv0301050

# 1.5. Document History

| Revision | Date       | Products/SW Versions                                              | Changes                                                                                                                                                                                              |

|----------|------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 2011-07-11 | /                                                                 | First issue                                                                                                                                                                                          |

| 1        | 2012-02-16 | /                                                                 | The present revision supersedes Rev. 0                                                                                                                                                               |

| 2        | 2013-05-31 | /                                                                 | Updated all the screenshots of the timing diagrams.  Added the AT commands list to set the codec in Slave-Burst (PCM)  Mode configuration.                                                           |

| 3        | 2013-06-20 | /                                                                 | The previous document title "HE910 Family Digital Voice Interface" has been changed in HE/UE910 Digital Voice Interface. In accordance with the new title, the Applicability Table has been updated. |

|          |            | /                                                                 | The previous document title "HE/UE910 Digital Voice Interface" has been changed in "HE/UE910, UL865 Digital Voice Interface".                                                                        |

| 4        | 2013-09-30 | Products added:<br>UL865-EUR / 12.00.xx4<br>UL865-NAR / 12.00.xx4 | /                                                                                                                                                                                                    |

| 5        | 2014-03-17 | /                                                                 | In the Applicability Table have been corrected the wrong products, turning them into UL865-EUR / 12.00.xx4 and UL865-NAR / 12.00.xx4                                                                 |

| 3        | 2014-03-17 | Products added:<br>UL865-N3G / 12.00.xx4                          | /                                                                                                                                                                                                    |

| 6        | 2014-04-16 | /                                                                 | The note about the Echo canceller has been added in chapter 2.  The chapters numbering/naming has been reorganized.                                                                                  |

# 1.6. Abbreviations and Acronyms

DTE Data Terminal Equipment

DVI Digital Voice Interface

GPIO General Purpose Input/Output

I<sup>2</sup>C Inter-Integrated Circuit

I<sup>2</sup>S Inter-IC Sound MSB Most Significant Bit

### 2. DVI Overview

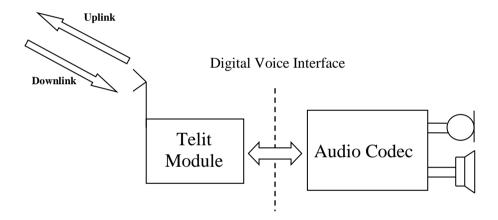

Before dealing with the configuration and technical aspects of the Telit' Digital Voice Interface (DVI) it is useful to illustrate briefly where and how this interface can be used, refer to fig. 1

The voice coming from the downlink, in digital format, is captured by the dedicated software running on the Telit's module and directed to the Digital Voice Interface. The Audio Codec decodes the voice and sends it to the speaker. The voice captured by the microphone is coded by the Audio Codec and directed through the Digital Voice Interface to the module that collects the received voice, in digital format, and sends it on the uplink.

fig. 1: Example of Digital Voice Interface Use

**NOTICE**: the Digital Voice Interface supports the Echo canceller functionality, which is beyond the scope of the present document. Refer to document [3] for the specific AT commands.

## 3. DVI Bus

The physical DVI interface provided by the Telit's modules is based on the I<sup>2</sup>S Bus. An overview of the standard I<sup>2</sup>S Bus is described in chapter 6.1. Tab. 1 summarizes the DVI signals and a short description for each one of them: refer to documents [1], [4], and [5] to have information on electrical characteristics and signals pin-out in accordance with the used module.

| DVI Signal               | DVI Signal name | Description       |

|--------------------------|-----------------|-------------------|

| Clock                    | DVI_CLK         | Data Clock        |

| Word Alignment           | DVI_WA0         | Frame Synchronism |

| serial audio data input  | DVI_RX          | Received Data     |

| serial audio data output | DVI_TX          | Transmitted Data  |

Tab. 1: DVI Signals

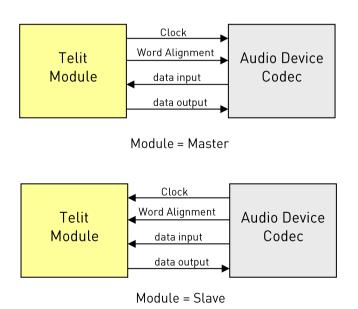

The figures below show the two configurations of the DVI interface relating to the Word Alignment and Clock signals. When the module is Master the Clock and Word Alignment signals (also called Word Alignment Output WAO) are generated by the module itself, otherwise, when it is Slave, both signals are generated by the connected Audio Device Codec.

In general, before establishing a voice call it is possible to select one of the two configurations and in accordance with the selected setting, configure the module and the codec via the AT commands provided by Telit, refer to documents [3]. The next pages describe the use of these AT commands.

fig. 2: Master and Slave Configurations

# 4. DVI AT Commands

Several DVI audio bus configurations are available via AT#DVI and AT#DVIEXT commands. The tables in the following sub-sections summarize their parameters; refer to documents [3] for AT commands syntax details.

### 4.1. AT#DVI

AT#DVI command enables/disables the DVI interface, selects the DVI port, and sets the module in Master or Slave configuration. The following table shows the AT command parameters values.

| AT#DVI = <mode>,<dviport>,<clockmode></clockmode></dviport></mode>                                                                   |                                       |                                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|--|--|

| <mode></mode>                                                                                                                        | <dviport></dviport>                   | <clockmode></clockmode>                          |  |  |

| <ul> <li>0 → disable DVI interface, factory setting for UE910 products</li> <li>1 → enable DVI interface, factory setting</li> </ul> | 1 → reserved<br>2 → select DVI port 2 | 0 → DVI slave<br>1 → DVI master, factory setting |  |  |

| for HE901 and UL865 products<br>2 → reserved                                                                                         |                                       |                                                  |  |  |

Tab. 2: DVI Configuration via AT#DVI command

## 4.2. AT#DVIEXT

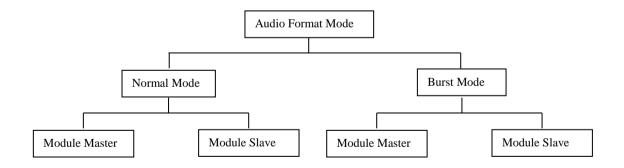

AT#DVIEXT command sets the module in Normal or Burst DVI Audio Format:

- In Normal DVI Audio Format the WAO signal defines the left and right audio channel.

- In Burst DVI Audio Format the WAO signal defines the beginning of the audio frame.

The following table shows the AT command parameters values.

| DVI Audio                 | ,,,,,,,,,,              |                                           |                                                                                             |                                                                                                          | diomode>, <edge></edge>                                                                                                                                                                                                                                                                                                                |

|---------------------------|-------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format<br>(Mode)          | <config></config>       | <samplerate></samplerate>                 | <samplewidth><br/>bit per sample</samplewidth>                                              | <audiomode></audiomode>                                                                                  | <edge></edge>                                                                                                                                                                                                                                                                                                                          |

| Normal (I <sup>2</sup> S) | 1<br>factory<br>setting |                                           | 0 → 16 bits per sample factory setting                                                      | 0 → Mono 1 → Dual Mono                                                                                   | <ul> <li>0 → the falling edge of the clock is used to shift out the next data to transmit. The received data bit is captured on the rising edge of the clock, factory setting.</li> <li>1 → reserved</li> </ul>                                                                                                                        |

| Burst (PCM)               | 0                       | 0 → 8 [KHz], factory setting 1 → 16 [KHz] | 1 → 18 bits per sample 2 → 20 bits per sample 3 → 24 bits per sample 4 → 32 bits per sample | In Dual Mono the same Data Word is transmitted on both audio channels (right and left). Factory setting. | <ul> <li>0 → the falling edge of the clock is used to shift out the next data to transmit. The received data bit is captured on the rising edge of the clock.</li> <li>1 → the rising edge of the clock is used to shift out the next data to transmit. The received data bit is captured on the falling edge of the clock.</li> </ul> |

Tab. 3: DVI Audio Format configuration via AT#DVIEXT command

# 5. DVI Setting Examples

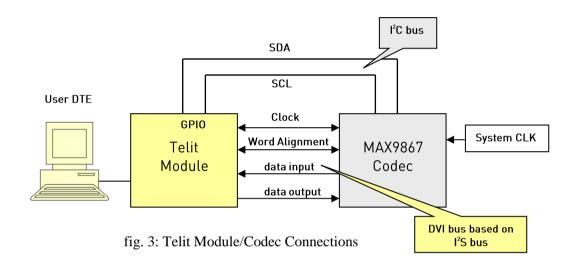

The next chapters show examples concerning the audio formats provided by the DVI audio bus in Master and Slave configurations. All the following setting examples are performed using the hardware configuration shown in fig. 3. I<sup>2</sup>C bus is used to configure the MAX9867 Codec<sup>2</sup> [2]: the user by means of suitable AT commands can control the codec. The DVI bus provides the voice connection between the two devices.

The setting examples are organized as shown in the figure below.

fig. 4: DVI Configurations

<sup>&</sup>lt;sup>2</sup> The following examples use the MAX9867 Codec, see chapter 6.2 for a schematic reference design. In general, the user can use any codec compliant with the technical requirements of the Telit's modules.

# 5.1. Normal Mode (I<sup>2</sup>S)

#### 5.1.1. Module is Master

The

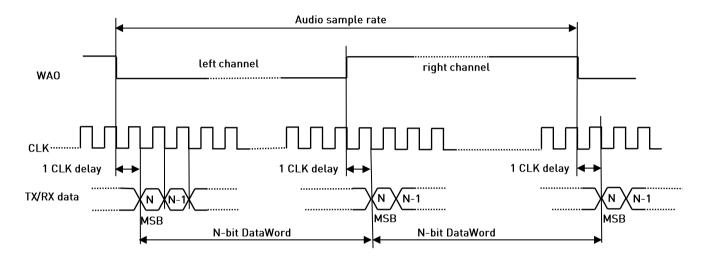

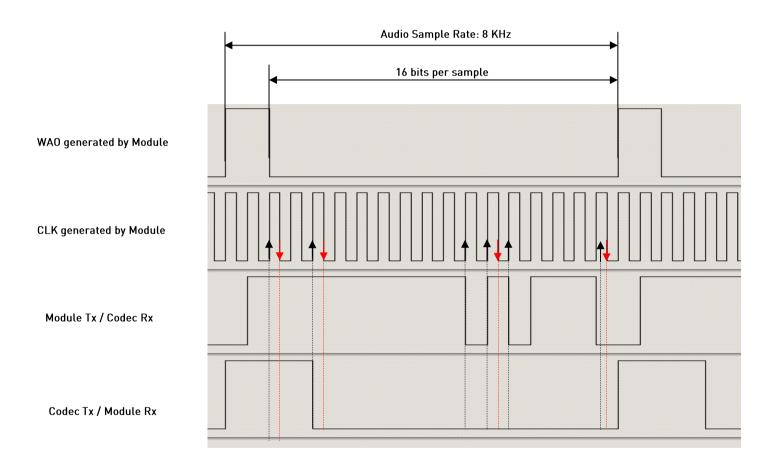

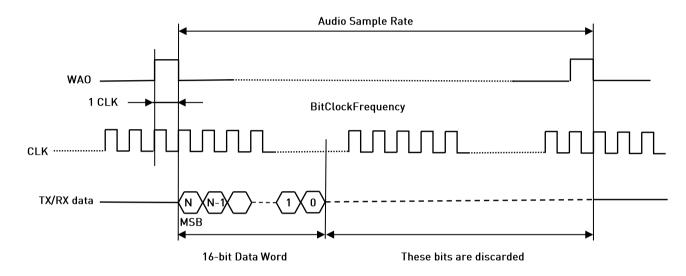

fig. 5 shows a timing diagram that refers to the module in the role of master. In this case, WAO and CLK signals are generated by the module. The WAO signal defines the frame of the two audio channels: left and right.

fig. 5: Module is Master/Normal mode/N bits per sample/Dual Mono

When module is Master the BitClockFrequency (CLK) is provided by the following expression:

$BitClockFrequency = DataWordBit \times ChannelNumber \times AudioSampleRate$

Refer to Tab. 4 for the BitClockFrequency generated by the Module.

|                             | Audia                      |           | AudioSampleRate  |               |

|-----------------------------|----------------------------|-----------|------------------|---------------|

| <samplewidth></samplewidth> | DataWordBit Audio channels | 8 KHz     | 16 KHz           |               |

|                             |                            | Chamilets | BitClockFre      | quency in KHz |

| 0                           | 16                         | 2         | 256              | 512           |

| 1                           | 18                         | 2         |                  |               |

| 2                           | 20                         | 2         | 384 <sup>3</sup> | 768           |

| 3                           | 24                         | 2         |                  |               |

| 4                           | 32                         | 2         | 512              | 1024          |

Tab. 4: BitClockFrequency generated by the module in Master/Normal Mode

<sup>&</sup>lt;sup>3</sup> The module generates 384 or 768 KHz also when the audio sample has 16 or 20 bits. In these configurations only 16 or 20 bits are taken in consideration, all other bits must be discarded.

Here are the lists of AT commands used to set the module in Master Normal (I<sup>2</sup>S) Mode, and configure the codec in accordance with the module setting. After each command is described the uses parameters values meaning.

#### Configure the Module in Master Normal (I<sup>2</sup>S) Mode

#### AT#DVI=1,2,1 OK

DVI bus

- 1 enable DVI interface

- 2 use DVI port 2 (mandatory)

- 1 set the module as Master (factory setting)

#### AT#DVIEXT=1,0,0,1,0 OK

- 1 Normal Mode (factory setting)

- 0 sample rate 8 KHz (factory setting)

- 0 16 bits per sample (factory setting)

- 1 Dual Mono, the same Data Word is transmitted on both audio channels (factory setting)

- 0 the falling edge of the clock is used to shift out the next data to transmit; the received data bit is captured on the rising edge of the clock. (factory setting)

#### Configure the codec in Slave Normal (I<sup>2</sup>S) Mode

I<sup>2</sup>C bus

#### AT#I2CWR=X,Y,30,4,19 >00109000100A330000330C0C09092424400060 OK

- X GPIO number used as SDA, refer to [3]

Y GPIO number used as SCL, refer to [3]

30 Device address on I<sup>2</sup>C, refer to [2]

- Device address on I<sup>2</sup>C, refer to [2]

Register address from which start the writing, refer to [2]

- 19 number of bytes to write

>00109000....refer to [2]

#### AT#I2CWR=X,Y,30,17,1

# >8A

#### OK

- X GPIO number used as SDA, refer to [3] Y GPIO number used as SCL, refer to [3]

- 30 Device address on I<sup>2</sup>C, refer to [2]

- 17 Register address where write data, refer to [2]

- 1 number of bytes to write

>8A, refer to [2]

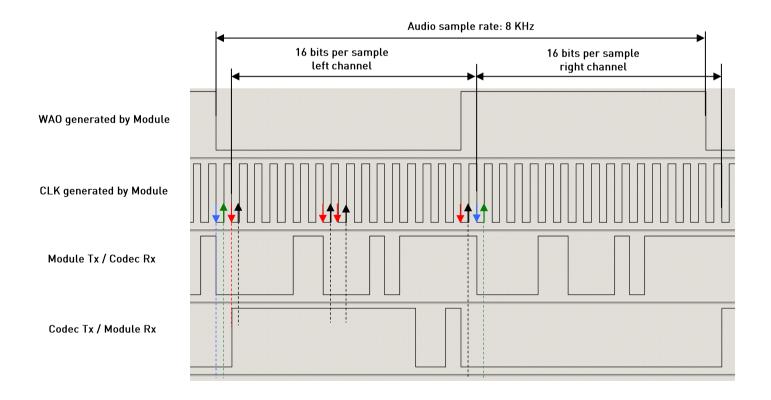

The fig. 6 shows the screenshot of the timing diagram, captured by a logic analyzer, using the above described module/codec setting. The CLK (256 KHz) and WAO signals are generated by the module.

#### Left channel:

$\downarrow$ : Data transitions occur on the falling edge of the CLK

†: Data are latched on the rising edge of the CLK

#### Right channel:

: Data transitions occur on the falling edge of the CLK

†: Data are latched on the rising edge of the CLK

fig. 6: Module is Master/Normal Mode/16 bits per sample/Dual Mono/<edge>=0

#### 5.1.2. Module is Slave

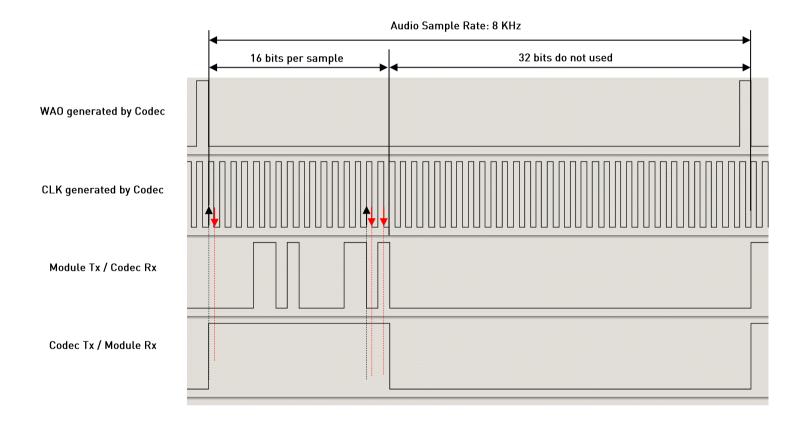

Here are the lists of the AT commands used to set the module in Slave Normal (I<sup>2</sup>S) Mode, and configure the codec in accordance with the module setting. After each command is described the used parameters values meaning.

#### Configure the module in Slave Normal (I<sup>2</sup>S) Mode DVI bus AT#DVI=1,2,0 OK enable DVI interface 2 use DVI port 2 (mandatory) set the module as Slave **AT#DVIEXT=1,0,3,1,0** OK Normal Mode (factory setting) sample rate 8 KHz (factory setting) 3 24 bits per sample Dual Mono, the same Data Word is transmitted on both audio channels (factory setting) 1 the falling edge of the clock is used to shift out the next data to transmit; the received data bit is captured on the rising edge of the clock. (factory setting)

#### Configure the codec in Master Normal (I<sup>2</sup>S) Mode I<sup>2</sup>C bus AT#I2CWR=X,Y,30,4,19 >001010009002330000330C0C09092424400060 OK X GPIO number used as SDA Y GPIO number used as SCL 30 Device address on I<sup>2</sup>C Register address from which start the writing 19 number of bytes to write >00101000....refer to [2] AT#I2CWR=X,Y,30,17,1 >8A OK X GPIO number used as SDA Y GPIO number used as SCL 30 Device address on I<sup>2</sup>C 17 Register address where write data number of bytes to write >8A, refer to [2] **NOTICE**: the codec is in Master configuration and generates a clock equal to 384 KHz. On the module the selected number of bits per sample is 24, see Tab. 4

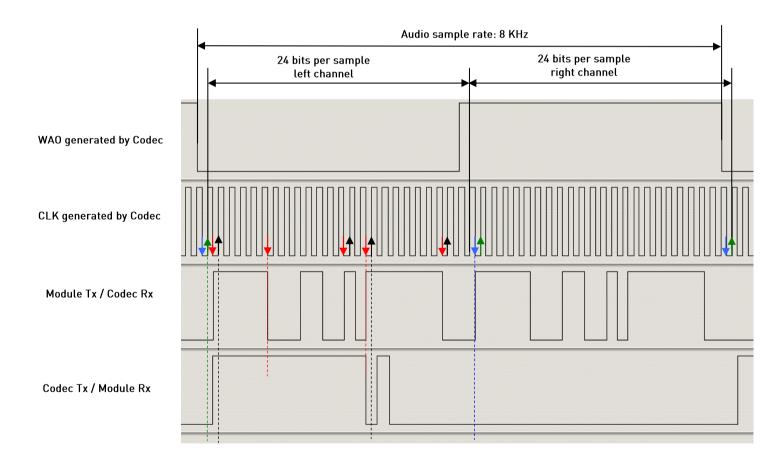

The fig. 7 shows the screenshot of the timing diagram, captured by a logic analyzer, using the above described module/codec setting. The CLK (384 KHz) and WAO signals are generated by the codec.

#### Left channel:

- : Data transitions occur on the falling edge of the CLK

- †: Data are latched on the rising edge of the CLK

#### Right channel:

- : Data transitions occur on the falling edge of the CLK

- †: Data are latched on the rising edge of the CLK

fig. 7: Module is Slave/Normal Mode/24 bits per sample/Dual Mono/<edge>=0

# 5.2. Burst Mode (PCM)

#### 5.2.1. Module is Master

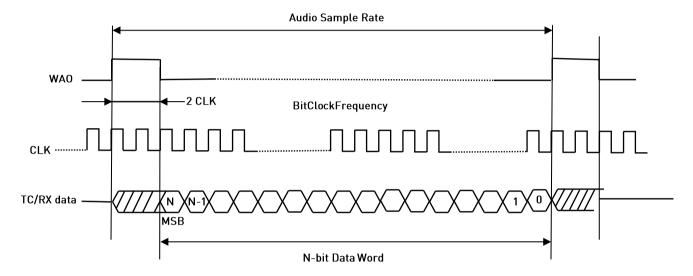

The fig. 8 shows a timing diagram that refers to the module in the role of master. In this case, the WAO and CLK signals are generated by the module. The WAO signal defines the frame of the audio channel.

fig. 8: Module is Master/Burst mode/N bits per Sample/Mono Mode

When module is Master the BitClockFrequency (CLK) is provided by the following expression:

$BitClockFrequency = (DataWordBit + 2) \times AudioSampleRate$

Refer to Tab. 5 for the BitClockFrequency generated by the module in accordance with the connected MAX9867 codec used in the examples.

|                             |             | AudioSampleRate  |               |  |  |

|-----------------------------|-------------|------------------|---------------|--|--|

| <samplewidth></samplewidth> | DataWordBit | 8 [KHz] 16 [KHz] |               |  |  |

|                             |             | BitClockFre      | equency [KHz] |  |  |

| 0                           | 16 (+ 24)   | 144              | 288           |  |  |

| 4                           | 32 (+ 2)    | 272              | 544           |  |  |

Tab. 5: BitClockFrequency in Burst Mode

<sup>&</sup>lt;sup>4</sup> The width of the WAO pulse is 2 CLK.

Here are the lists of AT commands used to set the module in Master Burst (PCM) Mode, and configure the codec in accordance with the current module setting. After each command is described the used parameters values meaning.

Configure the module in Master Burst (PCM) Mode. DVI bus **AT#DVI=1,2,1** OK enable DVI 2 use DVI port 2 (mandatory) DVI Master (factory setting) AT#DVIEXT=0,0,0,0,1 OK 0 Burst Mode sample rate 8 KHz (factory setting) 0 16 bits per sample (factory setting) 0 Mono Mode the rising edge of the clock is used to shift out the next data to transmit, the received data bit is captured on the falling edge of the clock

Configure the codec in Slave Burst (PCM) Mode.

I<sup>2</sup>C bus

#### AT#I2CWR=X,Y,30,4,19

#### > 00109000600A330000330C0C09092424400060

#### OK

X GPIO number used as SDA

Y GPIO number used as SCL

30 Device address on I<sup>2</sup>C

4 Register address from which start the writing

19 number of bytes to write

>00109000....refer to [2]

#### AT#I2CWR=X,Y,30,17,1

>8A

OK

X GPIO number used as SDA

Y GPIO number used as SCL

30 Device address on I<sup>2</sup>C

17 Register address where write data

1 number of bytes to write

>8A refer to [2]

The fig. 9 shows the screenshot of the timing diagram, captured by a logic analyzer, using the above described module/codec setting. The CLK (144 KHz) and WAO signals are generated by the module.

: Data transitions occur on the rising edge of the CLK

: Data are latched on the falling edge of the CLK

fig. 9: Module is Master/Burst Mode/16 bits per Sample/Mono Mode/<edge>=1

### 5.2.2. Module is Slave

The fig. 10 shows a timing diagram that refers to the codec in master configuration. In this case, the WAO and CLK signals are generated by the codec.

fig. 10: Module is Slave/Burst Mode/N bits per Sample/Mono Mode

Here are the lists of AT commands used to set the module in Slave Burst (PCM) Mode, and configure the codec in accordance with the current module setting. After each command is described the used parameters values meaning.

Configure the module in Slave Burst (PCM) Mode. DVI bus AT#DVI=1,2,0 OK enable DVI interface use DVI port 2 (mandatory) set the module as Slave AT#DVIEXT=0,0,0,0,1 OK 0 **Burst Mode** 0 sample rate 8 KHz (factory setting) 0 16 bits per sample (factory setting) 0 Mono Mode the rising edge of the clock is used to shift out the next data to transmit, the received data bit is captured on the falling edge of the clock

Configure the codec in Master Burst (PCM) Mode.

I<sup>2</sup>C bus

#### AT#I2CWR=X,Y,30,4,19 > 00101000A40A330000330C0C09092424400060 OK

- X GPIO number used as SDAY GPIO number used as SCL

- 30 Device address on I<sup>2</sup>C

- 4 Register address from which start the writing

- 19 number of bytes to write

>00101000....refer to [2]

#### AT#I2CWR=X,Y,30,17,1

>8A OK

- X GPIO number used as SDA

- Y GPIO number used as SCL

- 30 Device address on I<sup>2</sup>C

- 17 Register address where write data

- 1 number of bytes to write

- >8A refer to [2]

The fig. 11 shows the screenshot of the timing diagram, captured by a logic analyzer, using the above described module/codec setting. The CLK (384 KHz) and WAO signals are generated by the codec.

†: Data transitions occur on the rising edge of the CLK

: Data are latched on the falling edge of the CLK

fig. 11: Module is Slave/Burst Mode/16 bits per Sample/Mono Mode/<edge>=1

### 6. Annex

### 6.1. I<sup>2</sup>S Overview

This chapter provides a short description of the standard I2S bus. This standard suitably modified is used by the DVI interface implemented on the Telit's modules.

The standard I2S is an electrical serial bus designed for connecting digital audio devices. This popular serial bus has been developed by Philips® in 1986 as a 3-wire bus for interfacing to audio chips such as codecs. It is a simple data interface, without any form of address or device selection.

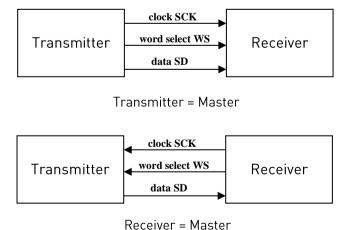

Refer to fig. 12: the I2S design handles audio data separately from clock signals. On an I2S bus, there is only one bus master and one transmitter.

In high-quality audio applications involving a Codec, the Codec is typically the master so that it has precise control over the I2S bus clock.

An I2S bus design consists of the following serial bus lines:

SD: Serial DataWS: Word Select

• Serial Clock: SCK

The I2S bus carries two channels (left and right) 8 bit long, which are typically used to carry stereo audio data streams. The data alternates between left and right channels, as controlled by the word select signal driven by the bus master.

fig. 12: I<sup>2</sup>S bus configurations

# 6.2. Schematic

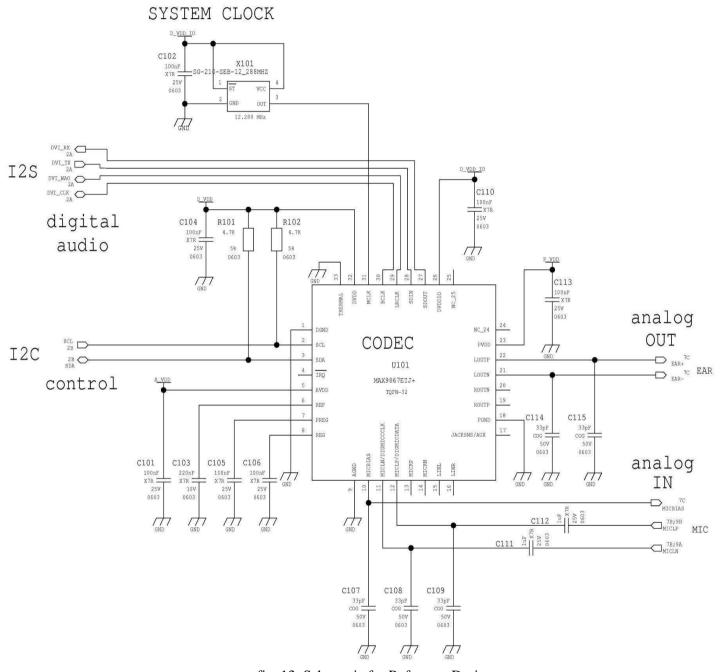

A schematic example of an interface between the Telit's modules and the MAX9867 CODEC could be the following:

fig. 13: Schematic for Reference Design